9 0 0 0 OA ストカスティック演算に基づく省エネルギー脳型LSI設計技術

- 著者

- 鬼沢 直哉 松宮 一道 羽生 貴弘

- 出版者

- 一般社団法人 電子情報通信学会

- 雑誌

- 電子情報通信学会 基礎・境界ソサイエティ Fundamentals Review (ISSN:18820875)

- 巻号頁・発行日

- vol.11, no.1, pp.28-39, 2017-07-01 (Released:2017-07-01)

- 参考文献数

- 70

- 被引用文献数

- 1

ストカスティック演算は,ソフトエラー耐性が高い演算方式として注目されているだけでなく,ある程度の誤りを許容可能なアプリケーション(画像処理,機械学習,ディープラーニング等)の増加に伴い,近年盛んに研究が行われている.本論文では,ストカスティック演算の基礎的な事項からハードウェア実現における利点・欠点について概説するとともに,ストカスティック演算の適用例として,脳の視覚情報処理を模倣した脳型LSIの実現例について幾つか紹介とともに,その省エネルギー性について議論する.

3 0 0 0 多進木網に基づく高速多値連想メモリ

- 著者

- 羽生 貴弘 樋口 龍雄

- 出版者

- 一般社団法人電子情報通信学会

- 雑誌

- 電子情報通信学会論文誌. D-I, 情報・システム, I-コンピュータ (ISSN:09151915)

- 巻号頁・発行日

- vol.76, no.2, pp.54-62, 1993-02-25

連想メモリは,大規模データベースシステム等のハードウェアエンジンとして極めて有用であり,近年の超微細加工技術の急速な発展を背景に,いっそうの高性能化が望まれている.しかしながら,通常の連想メモリにおける各種検索演算は,アレー構造に起因した逐次的処理に基づいて行われているため,データ語長に依存して処理速度が劣化するという問題点があった.本論文では,多進木網に基づいて検索演算の超高速化を図ると共に,それを多値電流モード回路で直接実現することにより,高性能な連想メモリを構成する方法を提案する.多進木網に基づく検索演算とは,各けたごとに検索演算が行われた結果に対し,それぞれ2進数のべき乗で重み付けをして線形加算することにより,大小比較演算を並列処理する方法である.多値電流モード回路の積極的活用により,本検索演算アルゴリズムで重要となる線形加算が結線のみで行えるため,全体として高密度な回路構成が可能となる.実際,本提案の構成方法に基づく4値連想モメリは,同等機能のものを通常の2値CMOS演算回路で実現した場合と比較し,2値ハードウェアと同程度の高速性を有しながら,2値実現の1/4程度のハードウェア量と動的消費電力で実現できることを明らかにしている.

2 0 0 0 OA 不揮発性素子を用いたPVTバラつきフリーVLSIシステムの基盤研究

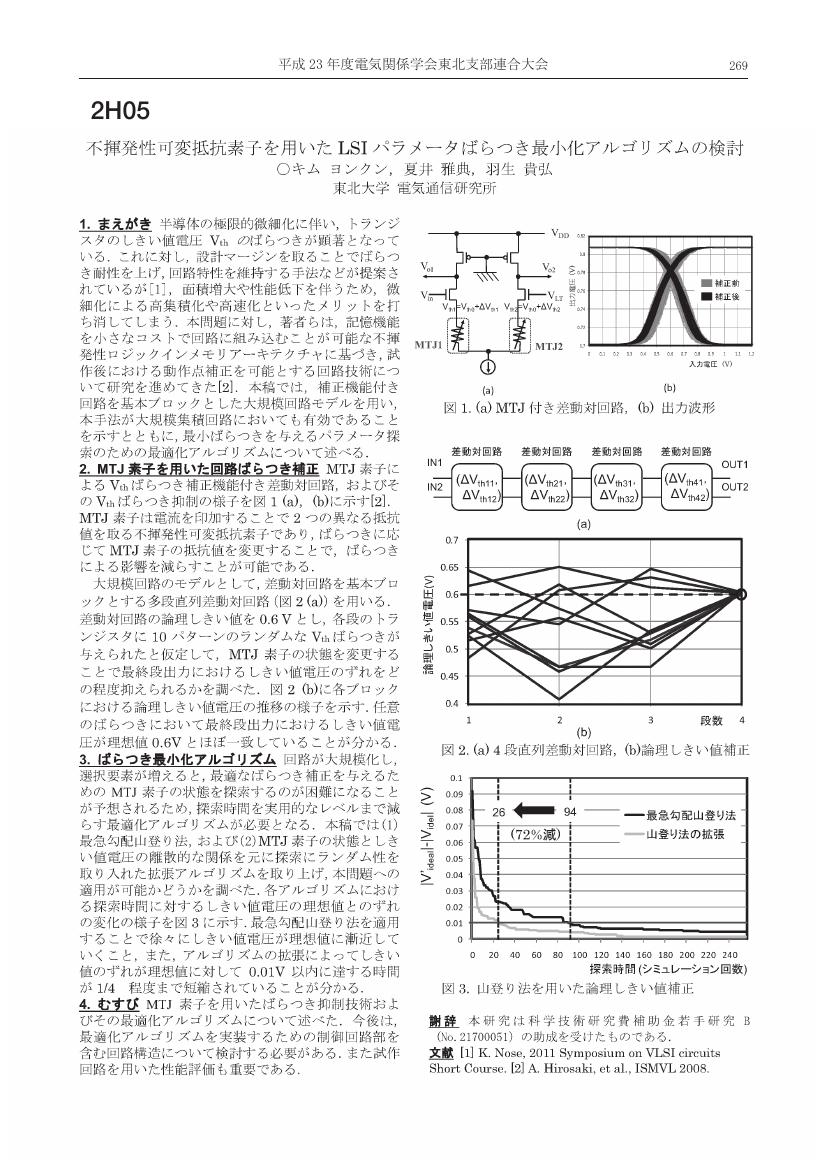

1 0 0 0 OA 不揮発性可変抵抗素子を用いたLSIパラメータばらつき最小化アルゴリズムの検討

- 著者

- キム ヨンクン 夏井 雅典 羽生 貴弘

- 出版者

- 電気関係学会東北支部連合大会実行委員会

- 雑誌

- 電気関係学会東北支部連合大会講演論文集 平成23年度 電気関係学会東北支部連合大会 講演論文集

- 巻号頁・発行日

- pp.269, 2011 (Released:2013-02-16)