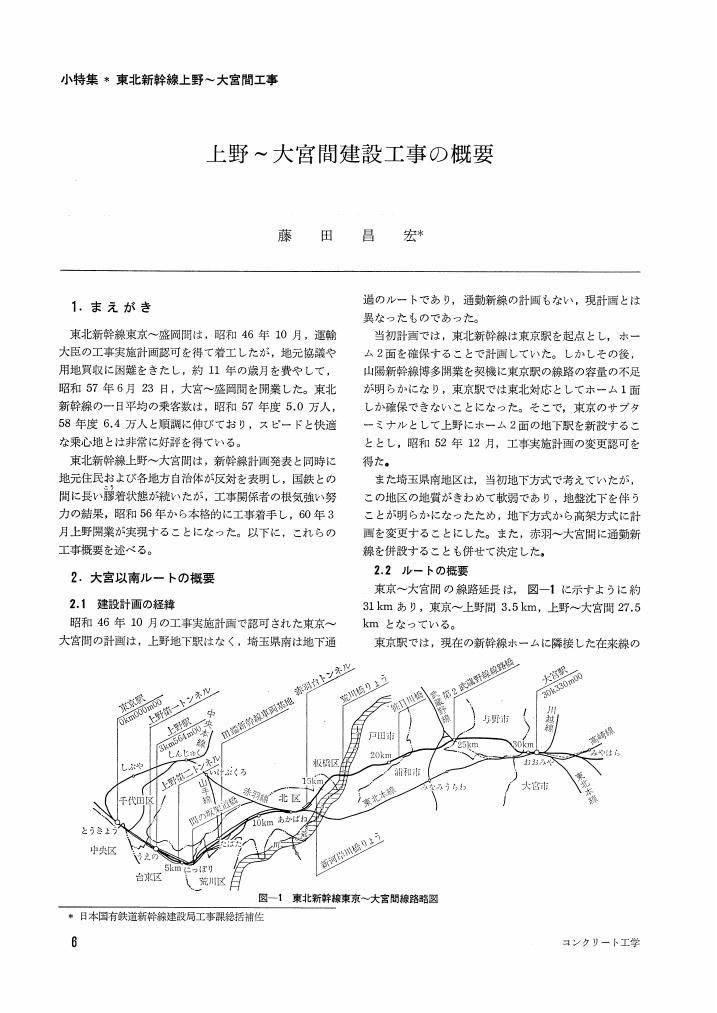

16 0 0 0 OA 東北新幹線上野~大宮間工事

- 著者

- 藤田 昌宏

- 出版者

- 公益社団法人 日本コンクリート工学会

- 雑誌

- コンクリート工学 (ISSN:03871061)

- 巻号頁・発行日

- vol.23, no.4, pp.6-9, 1985-04-01 (Released:2013-04-26)

1 0 0 0 IR 気管・気管支癌への高線量率管腔内照射

- 著者

- 池田 恢 井上 俊彦 藤田 昌宏 村山 重行 手島 昭樹 池添 潤平 竹内 規之 河野 伸明 小塚 隆弘 Ikeda Hiroshi Inoue Toshihiko Fujita Masahiro Murayama Shigeyuki Teshima Teruki Ikezoe Junpei Takeuchi Noriyuki Kohno Nobuaki Kozuka Takahiro イケダ ヒロシ イノウエ トシヒコ フジタ マサヒロ ムラヤマ シゲユキ テシマ テルキ イケゾエ ジュンペイ タケウチ ノリユキ コウノ ノブアキ コズカ タカヒロ

- 出版者

- 日本医学放射線学会

- 雑誌

- 日本医学放射線学会雑誌 (ISSN:00480428)

- 巻号頁・発行日

- vol.52, no.6, pp.841-843, 1992-06-25

1 0 0 0 多段論理合成における二段論理式簡単化の一手法

多段論理回路の簡単化手法のうち,多段回路の構造から生じたドントケア条件を考慮して簡単化を行なうBoolean minimizerと呼ばれるものがいくつか提案されている[1],[2],[3].このうち,文献[1] の手法は2段論理式簡単化プログラムESPRESSO-II[4]を利用したもので,どのような回路変換を行なうかというヒューリスティックに関しては場当たり的な変換を行なう他の手法に比べて効率的であるが,通常,多段論理回路の内部のドントケアを表現する2段論理式が巨大なものになってしまい,ドントケアそのものやその否定を扱うことが非常に困難になるという問題がある。そこで,本稿では2分決定グラフ(Binary Decision Diagram)[5]を用いて許容関数を表現しつつ,ESPRESSO-IIと同様のヒューリスティックを用いた2段論理式簡単化手法についての提案を行なう。

1 0 0 0 時相論理型言語Tokioを利用したハードウェア機能設計

- 著者

- 石川 悠司 Kang SeongWoon 李 蓮福 PARK GiLark 渡邊 翔太 瀬戸 謙修 小松 聡 浜村 博史 藤田 昌宏

- 出版者

- 一般社団法人電子情報通信学会

- 雑誌

- 電子情報通信学会技術研究報告. ICD, 集積回路 (ISSN:09135685)

- 巻号頁・発行日

- vol.106, no.550, pp.43-48, 2007-02-28

電子機器設計の分野では、新製品を市場に早く投入するため設計期間の短縮が強く求められる。この要求に対して、既存の設計を再利用する設計手法は極めて有効である。設計再利用の中で既存設計データベースの果たす役割は大きく、既存設計の仕様を表現する方式は非常に重要である。本研究で提案する仕様表現手法は、XMLベースの表による情報の列挙とUMLベースの直感的な図示を組み合わせることで、設計者が回路ブロックの仕様を理解するのを助ける。さらに、ルールベースの検証手法を導入することで、仕様記述に誤りが入り込む可能性を減らす。また、ケーススタディとして、ロボットの制御回路から取り出した回路ブロックに対して仕様記述を作成した。

- 著者

- 石川 悠司 Kang SeongWoon 李 蓮福 PARK GiLark 渡邊 翔太 瀬戸 謙修 小松 聡 浜村 博史 藤田 昌宏

- 出版者

- 一般社団法人電子情報通信学会

- 雑誌

- 電子情報通信学会技術研究報告. VLD, VLSI設計技術 (ISSN:09135685)

- 巻号頁・発行日

- vol.106, no.547, pp.43-48, 2007-02-28

- 被引用文献数

- 3

電子機器設計の分野では、新製品を市場に早く投入するため設計期間の短縮が強く求められる。この要求に対して、既存の設計を再利用する設計手法は極めて有効である。設計再利用の中で既存設計データベースの果たす役割は大きく、既存設計の仕様を表現する方式は非常に重要である。本研究で提案する仕様表現手法は、XMLベースの表による情報の列挙とUMLベースの直感的な図示を組み合わせることで、設計者が回路ブロックの仕様を理解するのを助ける。さらに、ルールベースの検証手法を導入することで、仕様記述に誤りが入り込む可能性を減らす。また、ケーススタディとして、ロボットの制御回路から取り出した回路ブロックに対して仕様記述を作成した。

1 0 0 0 OA 高位合成ツールを利用したハードウエアアルゴリズムの最適化

- 著者

- 福井 啓 藤田 昌宏

- 雑誌

- 研究報告システムLSI設計技術(SLDM)

- 巻号頁・発行日

- vol.2011-SLDM-150, no.10, pp.1-6, 2011-05-11

近年大規模・高速化が求められる、HPC(High Performance Computing) の分野において、順調な大規模化が進む FPGA(Field Programmable Gate Array) を用いて実現しようという研究が報告されている。本研究は FPGA を用いて、特定分野における数値計算の高速化の実現を目指したものである。一般に計算アルゴリズムを FPGA 上で実装するには時間がかかる、また大きな労力が必要である。本研究では主要な計算部分はデータフローグラフを書くことによってハードウエアを記述できる高位合成ツールを用いており、開発期間の短さを利用して様々な実装の比較をした。本発表では、津波のシミュレータの実装を通して、様々な実装やアーキテクチャを速度の観点から比較をする。

1 0 0 0 OA 反例と設計分割に基づく高位設計に対する効率的な設計修正支援手法

- 著者

- 原田 裕基 松本 剛史 藤田 昌宏

- 雑誌

- 研究報告システムLSI設計技術(SLDM)

- 巻号頁・発行日

- vol.2011-SLDM-150, no.12, pp.1-6, 2011-05-11

高位設計記述において、シミュレーションや形式的手法によって機能仕様に反する実行例(反例)が発見された場合、その反例や機能仕様を参照しながら、設計記述をデバッグする必要がある。本稿では、このように反例に基づくデバッグ作業を支援する手法を提案する。具体的には、与えられた反例および正しい実行例から、全てのテストパタンを正しく実行するための設計記述修正の候補を形式的に求める。これにより、設計者は、修正すべき箇所と修正方法の候補を得ることができ、より効率的にデバッグ作業を行えることが期待できる。提案手法では、反例入力パタンによって正しい実行結果を得るためには、どの変数値を実行値とは異なる値に置換すれば良いか、を SMT ソルバーを用いて解いている。加えて、効率的に修正候補を求めるために、設計を分割し、部分的にこれを適用する手法を提案する。実験により、提案手法によって、設計中の設計誤りを正す修正を求めることがでることを示す。

1 0 0 0 電子機器用解析技術のシステムバイオロジーへの応用

本研究では、従来からハードウェアの設計支援や設計検証に用いられてきた手法によって、近年注日を集めているシステムバイオロジーにおけるシミュレーションや解析を効率的に行い、実験室で行う実験では観測が困難な現象の観測や生化学反応における内部状態の推定を実現することを目的としている。今年度は、まず、昨年度の一般的な調査の続きとして、ハードウェア実装による生化学システムのシミュレーションの高速実行に着目し、特に詳細な調査を行った。その結果として、既存研究lこよりNext Reaction Method(NRM)までの手法は高速なハードウェア実装が既に提案されており、それらにおいては浮動小数点演算処理の最適化が重要であることが分かった。次に、上記の調査結果を踏まえて、NRMよりも高速なシミュレーション手法であるTau Leaping(TL)に着目し、その高速なハードウェア実装について検討した。反応を一つずつ逐次処理しているNRMに対して、TLでは複数の反応が一つの時間区間で起こり得ることを前提としてそれらをまとめて処理している点に特徴がある。したがって、複数の反応を並列に処理することが可能であり、よりハードウェア実装に適していると考えられる。さらに、一つの反応あたりの除算処理数もNRMより少ない点も、ハードウェア実装に有利である。ただし、TLにはNRMには無い微分処理が含まれているが、差分式に近似して処理を行うことにより高速に実行可能である。比較実験として、実際のソフトウェアの生化学シミュレータであるStockSimによるシミュレーションと、FPGAであるVertex5によるハードウェア実行との比較を考えており、現在までにその環境構築が完了している。今後は、実際にシミュレーション速度を比較することにより、提案するハードウェア実装による高速化できていることを確認する予定である。

論理回路設計を支援する場合に,ハードウェア記述を様々なレベルから,formalにおこなうことが重要である。Tokioは,時相論理(LITL)にもとづき,高度に抽象的なレベルからハードウェア記述をおこなうことができる。我々は,これまで各種のハードウェアをTokioにより実際に記述し,いくつかの記述に対して検証をおこなってきた。しかし,論理式による記述は,形式的に完全であるが,記述の階層化に問題がある。論理式自体が平坦な為に全体の記述が平坦になってしまう。この間題は,Cや,Prolog, Lispなどのプログラミング言語にも共通した問題である。ここでは,Tokioのプログラムの基本形であるClausal Formに,命題論理式を付け加えて,ハードウェアの同期部と機能部の記述を分離することを考察する。これにあわせて,Tokioの記述をモジュール化するために,オブジェクト指向の記述を導入する。これにより,平坦な記述を避けることができ,より実用的な記述が可能となる。